-

Dubhe-90

High Performance 64-bit RISC-V Processor

data centers, PC, mobile devices, high-performance network communications, and machine learning

-

Dubhe-83

Follows the RVA23 Profile, supports RVV1.0 and supports all extensions of Vector Crypto

mobile, desktop, AI, and automotive

-

Dubhe-80

64-bit application processor for energy-efficient computation

mobile, desktop, AI, and automotive

-

Dubhe-70

ultra-low power consumption out-of-order commercial-grade 64-bit RISC-V CPU IP

mobile, desktop, and AI

-

StarNoC-500

StarFive's first self-developed interconnect fabric IP with cache coherence support

supporting the construction of multi-cores and SoC to provide cache coherence NoC

-

StarNoC-700

StarFive's self-developed interconnect fabric IP with cache coherence support

supporting cache coherence, enabling the construction of manycore SoC solution

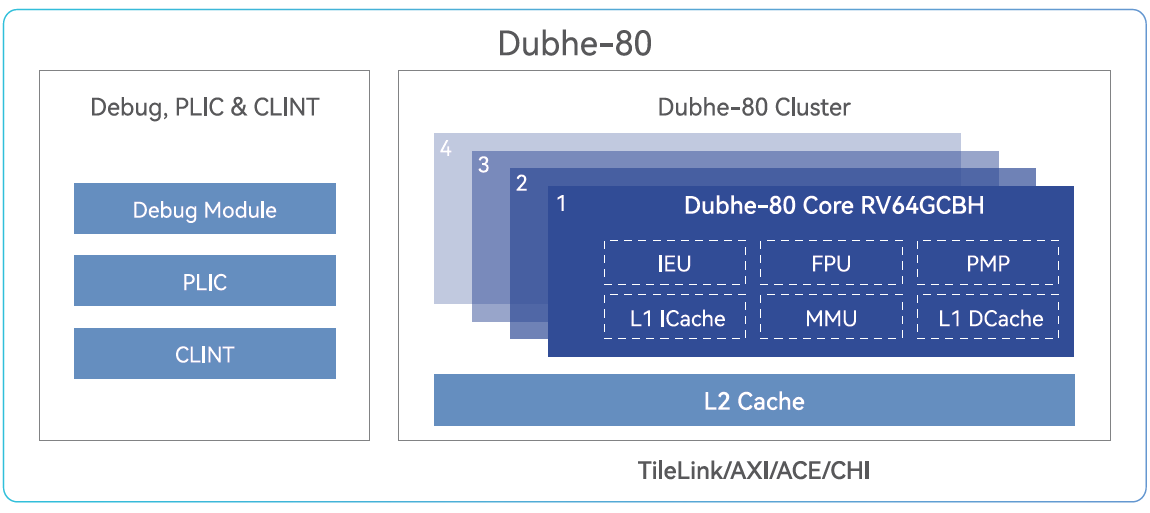

Dubhe-80

StarFive Dubhe-80 processor features a 9+ stage, 3-issue, out-of-order pipeline, fully compliant with a rich set of RISC-V extensions of RV64GCBH_Zicond_Zicbom_Zicboz_Zicbop. With a score of 8.5 SPECInt2006/GHz, Dubhe-80 is designed for mobile, desktop, AI, and automotive applications that require highly energy-efficient computation. Dubhe-80 has been pre-integrated and verified, making it easy to use for SoC development work. With options of single-core, dual-core, or quad-core in a single cluster with memory coherency, Dubhe-80 is highly scalable.

Key Features

Follows the RVA23 profile

SPECint2006: 8.5/GHz

Dhrystone: 6.0/Mhz (Legal)

RV64GCBVH

9+ stage, 3-issue pipeline

Superscalar, deep out-of-order execution

Support for multi-core cache coherence

Applications

Mobile Application

- Mobile phone

- Tablet

- Smart wearables

- Gaming devices

Industry Control

- HMI

- Industry display

- Industry inspection

- Smart gateway

AI

- Robotics

- Computer vision

- Smart Home